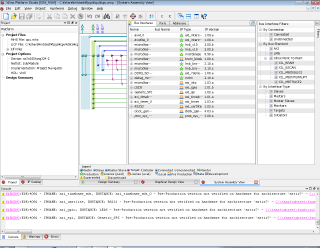

XPSのメイン画面での操作

18. XPSのメイン画面が出ます。

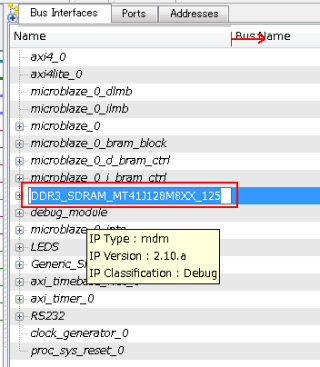

19. まずはメモリコントローラをカスタマイズします。Nameとかかれた欄の枠を引っ張って広く見やすくしたら、DDR3_SDRAM…を選択してF2キーを押せば、名前が変更できます。まずは名前をDDR3_SDRAM_MT41J256M8XX_15に直しましょう。

MIGによるメモリのカスタマイズ

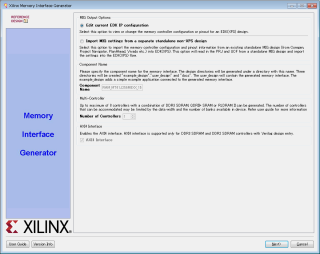

20. このDDR3_SDRAM…をダブルクリックすると、MIGが起動します。

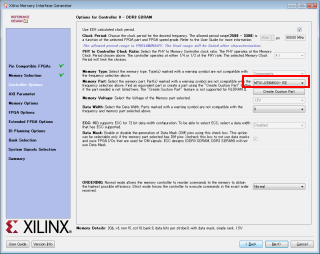

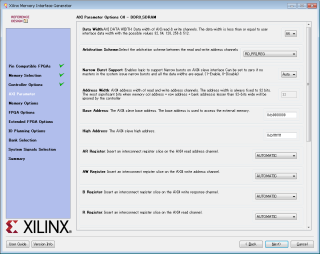

21. Nextを3回押すと、次のダイアログになります。ここでメモリの型番をMT41J256M8XX_15Eに変更します。

それ以外は設定する必要はありません。

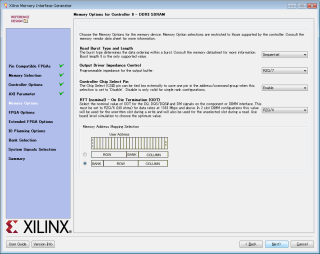

22. 次のダイアログも変更箇所はありません。

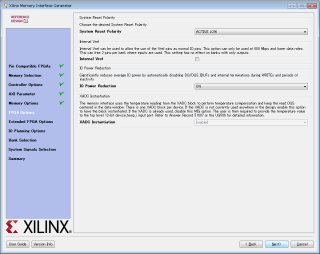

23. その次のダイアログも変更はありません。

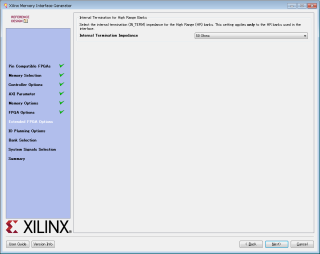

24. その次のダイアログも変更はありません。

25. その次のダイアログも変更はありません。

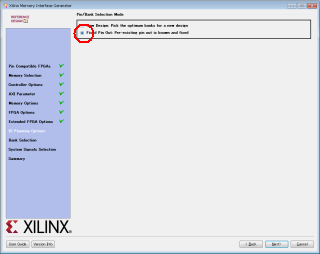

26. 次のダイアログではFixed Pin Outを選択します。

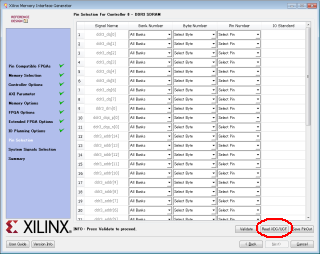

27. 次の画面が出るので、Read UCF/XCFを押します。

ファイルを選択するダイアログがでるので、Artix7-ddr3プロジェクトに入っているUCFファイルを読み込ませます。

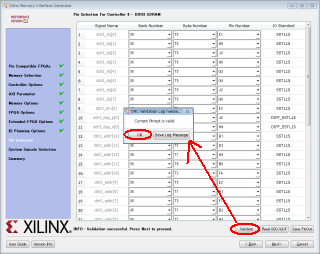

28. UCFファイルが読み込まれたら、Validateを押して、OKを押します。

29. Next -> Finishを押せばDDR3の設定は完了です。元の画面に戻ってきます。

この一連の作業では、DDR3メモリの型番を変更し、ピン配置を固定しました。

クロックの設定

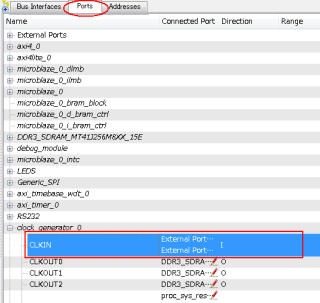

30. Portタブを選択し、Nameを引き伸ばし、clock_generator_0を展開します。

中に2つのExternal Port..が見えるはずです。

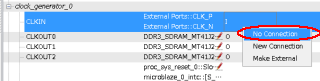

31. ここでNo Connectionを選び、削除します。

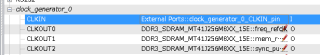

32. 次にMake Externalとやれば、新しい「clock_generator_0_CLKIN_pin」というポートが生成されます。

これで、Differentialのポートを削除し、SingleEndのポートが生成されました。

SPIの設定

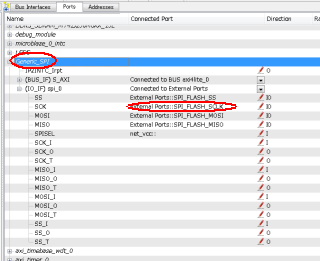

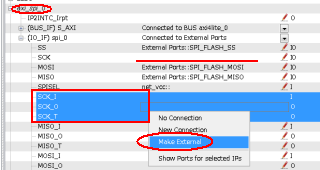

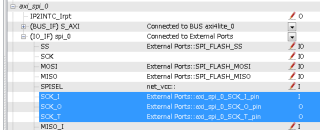

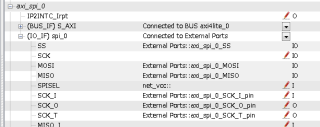

33. 次にGeneric_SPIのポートを展開します。

このGeneric_SPIという名前を、axi_spi_0に変更し、ポートSCKを削除します。

34. 代わりに、SCK_I、SCK_O、SCK_Tを選択して、Make Externalをやります。

35. SPIのクロックは、inoutの信号ではなく、入力、出力、出力制御と3つのばらけました。

36. ついでに、SSやMOSIなどの信号名も合わせて変更しておきます。

これでSPIの信号を外に出す設定も完了です。

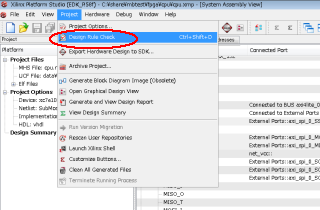

37. メインのメニューから、Project→Design Rule Checkを行います。

Errorが出なければOKです。

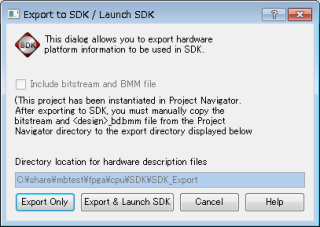

38. 次に、Project→Export Hardware Design to SDKを実行します。

次のダイアログが出るので、Export & Launch SDKを押して、しばらく待ちます。

エクスポートされたハードウェアのSDKでの確認

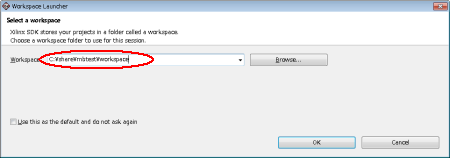

39. XPSの裏でSDKが起動します。Eclipseベースなので、「Workspaceはどこか?」と聞いてきます。

FPGAのデザインをしているディレクトリの横に新しく作るように指示すればよいでしょう。

ここではC:¥share¥mbtest¥workspaceと指定しました。

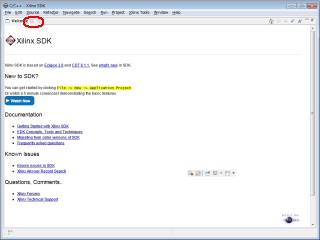

40. Welcome Xilinx SDKと書かれた画面が出るので、ページの×を押して閉じます。

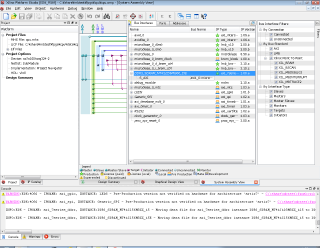

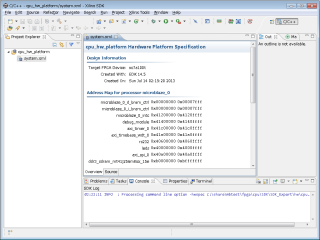

41. すると、裏にこんな画面が隠れています。

これが出れば成功です。ひとまずSDKは終了して構いません。

なお、手順38でExport Onlyを押すとここまで一気にはこれません。SDKの中でNew→Other→Hardware Platform Specificationという手順を踏まなければならないので面倒です。Export & Launch SDKを押しておきましょう。

ここまでくれば、XPSでの操作は終わりです。

XPSは閉じてください。(保存の必要はありません)