仕様と特徴

ご案内

このWebサイトはCosmo-Zの古い情報サイトであり、

最新の仕様とは異なる情報が掲載されている可能性があります。

Cosmo-Zの最新の仕様や使用方法、開発方法については、

特設サイト https://cosmoz.jp/ に移動しました。

新しいサイトへお越しください。

ハードウェアの仕様と特徴

アナログ部

- 12bit版(標準品)

- ADコンバータ・・・12bit 105MHz ADC8ch

- 入力フルスケール ±0.5V

- 入力フィルタ・・・2次LPF カットオフ周波数50MHz

- 入力換算ノイズ・・・200μVpp

- 歪率・・・-70dB以下 (typ)

- 16bit版(高精度品)

- ADコンバータ・・・16bit 125MHz ADC8ch

- 入力フルスケール ±0.5V

- 入力フィルタ・・・2次LPF カットオフ周波数50MHz

- 入力換算ノイズ・・・40μVpp (ディジタルフィルタ使用)

- 歪率・・・-70dB以下 (typ)

ディジタル部

- 拡張コネクタ・・・シングルエンド信号を106本 (その内LVDS48組)

- ギガビットトランシーバ・・・XILINX GTXポートを2組(6.0Gbps)

- 通信機能・・・PCI Express Gen2×1、USB3.0、ギガビットイーサ

- USB3.0の通信速度は、入出力ともに350MByte/sec程度

- 標準構成ではUSB3.0は使用しないので、お問い合わせください

- ギガビットイーサの通信速度

- 1000Base接続時に、TCP/IPで66MByte/s

- 100Base-TX接続時には、TCP/IPで12MByte/s弱

- USB3.0の通信速度は、入出力ともに350MByte/sec程度

FPGAの機能

- 単純なデジタイザ/データロガー(105MHz 8chで最大0.3秒間)

- 最大計測時間はチャネル数と速度によって変わります

- パルス波形計測回路(イベントが発生した場合のみ記録する)

- テスト波形発生回路

オプション機能

- 放射線信号処理回路(DSP)

- TFA、CFD、BLR、Trapezoidal Shaper、PeakHold、LinearGateなど

- 32ch MCA(マルチチャネルアナライザ)

- ハードウェア・ロックイン・アンプ

- ハードウェア・フーリエ変換器

電源

- DC5V単一電源またはPower Over Ethetで動作

- 定格消費電力 7~10W (5V 1.4A~2A) ※FPGAの構成によって変わります

基板サイズ

- 88mm×175mm

基板の構成

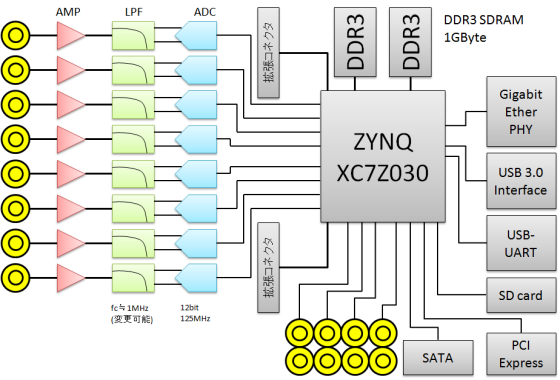

Cosmo-Zのメイン基板は下の図のような構成になっています。

メイン基板では、8chのアナログ入力を同時にサンプリングしてディジタル信号に変換し、FPGA(ZYNQ XC7Z030)へ送ります。

ZYNQとホストPCとの間は、通常はGigabit EtherかUSB-UARTで接続します。通常は使用しませんが、USB3.0などでインタフェースできるほか、SATA、PCI Express(Gen2 x1)などの高速I/Oも備えています。

アナログ入力は50Ωの入力インピーダンスで、フルスケールは±0.5Vです。アナログフィルタは、カットオフ周波数が約50MHzとなるようなLPFを入れています。カットオフ周波数の変更も承ります。

FPGAとソフトウェアの仕様と特徴

Cosmo-ZのFPGAの構成は用途に応じて変化しますが、基本的な構成は下の図のようになっています。

ADCで計測したデータは、FPGA内でデコードされ、インタコネクトを経由してメインメモリに格納されます。この経路にディジタル信号処理回路を挿入することで、波形の特徴をFPGA内のロジックでリアルタイムに抽出することができます。また、計測回路を挿入することで統計などのデータを取ることができます。

信号処理回路には、

- 放射線信号処理回路 DSP(TFA、CFD、Shaper)

- ディジタル・ロックインアンプ

- リアルタイム高速フーリエ変換回路

などがあります。

また、計測回路には

- MCA(マルチチャネルアナライザ)

- 波形計測記録回路

などがあります。

放射線および粒子検出向け信号処理回路(DSP)

Cosmo-ZのFPGAには最大32chの下の図のような「放射線信号処理回路(DSP)」を入れることができます。

- TFA(Timing Filter Amplifier) パルスを鋭くする。ポールゼロで歪を取る

- BLR(Base Line Restorer) すばやくゼロに戻す

- CFD(Constant Fraction Discriminator) 正確なタイミングの検出に

- Trapezoidal Shaper 台形型波形整形回路 弾道欠損などの補正に使う

- GateGenerator 任意の長さのトリガを発生させる

- LLD/ULD ディスクリの設定

波形計測回路

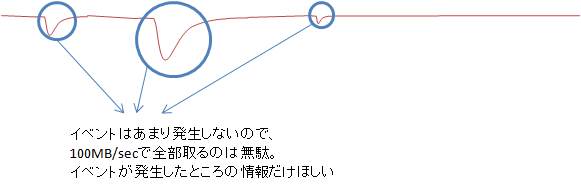

イベントがごく短時間に発生し、他はゼロになっているような信号を扱う場合、すべての期間のデータを記録すると無駄が発生します。

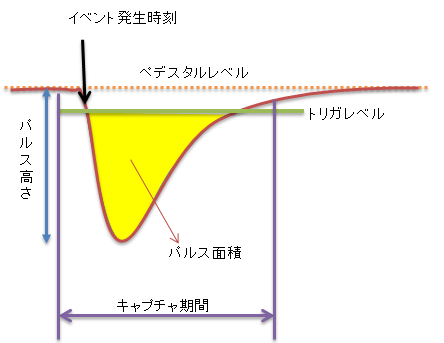

信号の発生した期間に当該チャネルの波形だけを収集するのが波形計測回路です。例えば、下の図のような波形が入力された場合、Cosmo-Zの計測回路はトリガの前後の期間のパルス波形をキャプチャします。

そして、イベントが発生したときの、ADCの番号、時刻(10ns単位で48bit)、パルス高さ、パルス面積、ペデスタルレベル(ベースライン)、トリガレベル、キャプチャ時間等の情報を「ヘッダ」として波形データの先頭に付加します。

仕様

- 記録長・・・ 標準構成では最大998ポイント (約12μ秒)

オプションで最大8010ポイント(約100μ秒) - デッドタイム・・・1回の計測で100ns以下

- タイムスタンプの形式・・システム起動時からのクロック数を10ns単位で記録

- 計測される値・・・パルスのピーク値、パルスの面積、トリガ時間、無信号時のレベル、他

- 精度・・・ADCの精度による

- ヘッダ長・・・24バイト

- データ長・・・0~998または0~8010ワード (1ワード=2バイト)

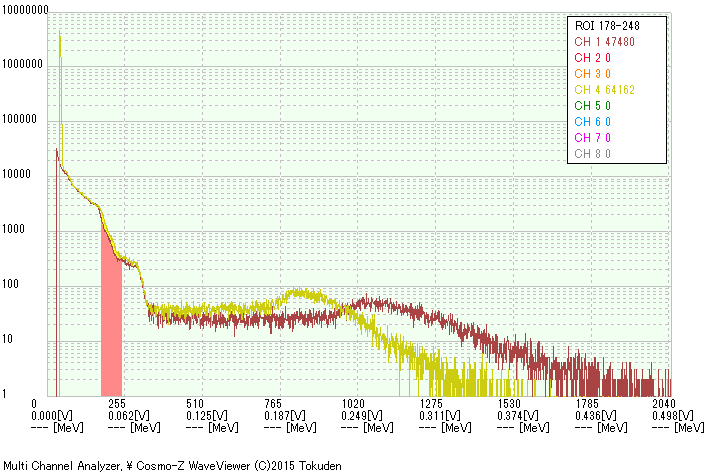

マルチチャネルアナライザ(MCA)

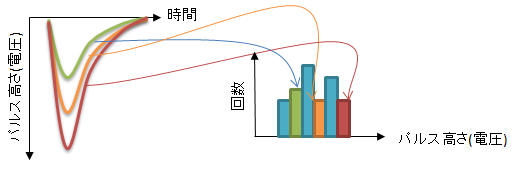

マルチチャネルアナライザ(MCA)とは、入力したパルスの高さを、頻度で表したヒストグラムとして記録するものです。

この機能によって、何Vの波高のパルスが何回来た、というグラフが得られます。

波高の高いパルスはグラフで右の方に記録され、波高の低いパルスは左の方にに記録されます。

Cosmo-ZのMCAは、横軸は最大2047、縦軸は最大4294967295(=232-1)までカウント可能です。このMCAは最大32個インプリメントすることができ、完全に独立して同時動作が可能です。

MCAはハードウェアで処理されるため、毎秒1Mカウント/chを超える計測であってもオーバーフローしたり、デッドタイムが増えるということはありません。

ディジタル・ロックイン・アンプ

微弱な信号を精度よく検出するための測定回路です。

ノイズに埋もれた微弱な信号でも、その信号がある周波数に同期していれば、sin cosと乗算して長時間積分することで、ノイズ成分は打消しあるため、元の信号を復元することができます。

動作イメージ(クリックで拡大)

ディジタル・ロックイン・アンプ仕様

- ロック可能周波数 4.8Hz~1MHz

- 入力チャネル数 3ch

- 演算精度 24bit

- A/D変換分解能 12bit

高速フーリエ変換回路

特殊電子回路の開発したFFT IPコアは、32768ポイントのFFTを、最短51μ秒で実行します。Radix-8、周波数間引き、改良型FFTアルゴリズムを採用しています。

FPGAのリソースは、BRAM36Kを96個、DSP48Eを216個使用します。Cosmo-Zに8chのキャプチャ回路など諸々一式を入れた状態でのリソースの使用率を示します。

| Slice Logic Utilization | Used | Available | Utilization |

| Number of Slice Registers | 15,302 | 15,720 | 9% |

| Number of Slice LUTs | 11,431 | 78,600 | 14% |

| Number of occupied Slices | 4,874 | 19,650 | 24% |

| Number of RAMB36E1/FIFO36E1s | 140 | 265 | 52% |

| Number of RAMB18E1/FIFO18E1s | 82 | 530 | 15% |

| Number of DSP48E1s | 224 | 400 | 56% |

FPGAに入れても圧迫しないコンパクトな設計になっています。

1回の32768ポイントFFTを51μ秒で実行できるので、連続した時系列データをFFTした場合、最高80MHzまで切れ目なくできる計算になります。