FPGAプロジェクト

FPGAのデザインは、2種類あります。

- PCIe-DMA シンプルなBRAM読み書きデザイン 2017/9/4

- PCIe-DMAでDDR3メモリを読み書きするFPGAデザイン 2018/4/4

このページでは前者のシンプルなBRAM読み書きのPCIe-DMAデザインについて説明します。DDR3メモリを読み書きするデザインは応用編としてこちらに記載しています。

ZIPファイルを解凍すると、cosmok-xdma3とip_repoという2つのフォルダが入っています。cosmok-xdma3の中にcosmok-xdma3.xprというVivadoのプロジェクトファイルが入っているので、これをダブルクリックしてVivadoを起動します。

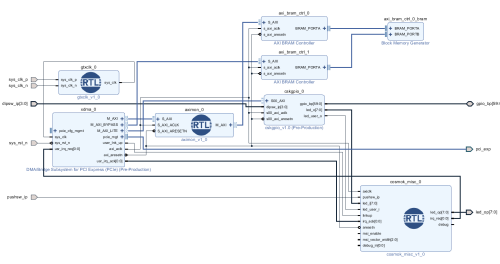

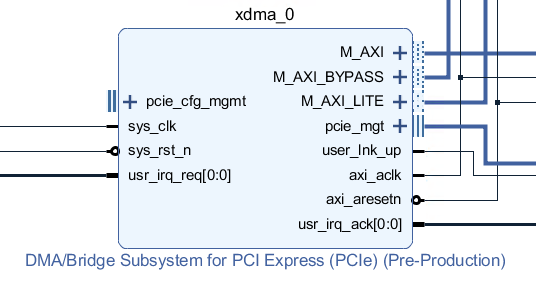

FPGAのブロックデザインは、以下のような構造になっています。

モジュールの説明

このサンプルデザインには以下のモジュールが含まれています。

| モジュール名 | 機能 |

|---|---|

| gtxclk | ボード上のGTXクロックをFPGAのメインクロックとして使用するためのモジュールです。 |

| xdma | XILINXのPCI Express DMAコアです。(XDMA) |

| aximon | MITOUJTAGでAXIの信号をモニタするためのJTAG-ロジアナコアです。必要なければ削除可能です。 |

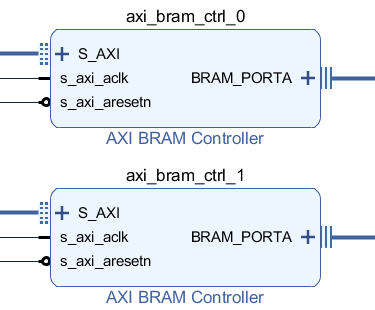

| axi_bram_ctrl | AXIバスをBRAMを接続するためのプロトコル変換コアです。 |

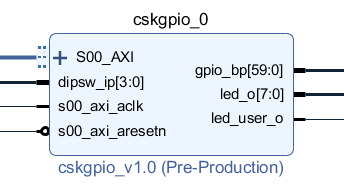

| csk_gpio |

Cosmo-K用のGPIOコアです。GPIOだけではなく、ボード上のGPIOやLED、DIP SWの制御と、内蔵レジスタの実装、バージョン番号の管理を行っています。 |

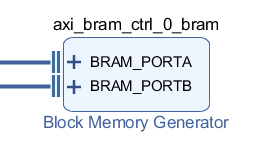

| axi_bram_ctrl0_bram | Block Memoryの本体です |

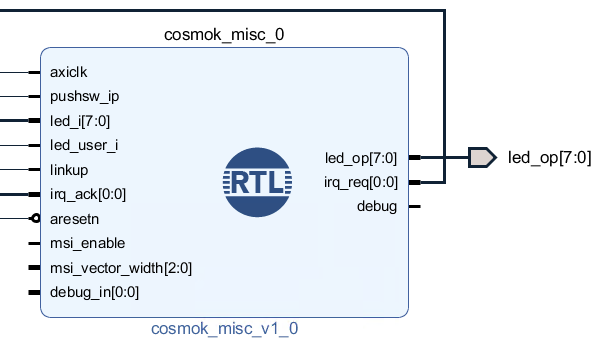

| cosmok_misc | 主にデバッグのための雑多な機能が入ったモジュールです。必要なければ削除可能です。 |

以下、簡単に各モジュールの動作を説明します。

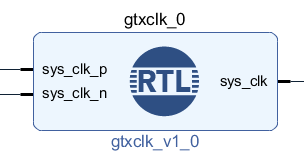

gtxclk

内部でIBUFG_GTXを実装して、PCI Expressの100MHz作動リファレンスクロックをシングルエンドに変換しています。

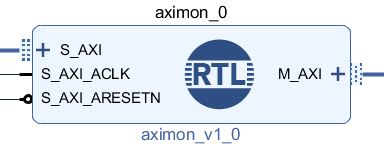

aximon

MITOUJTAGで、ChipScopeのようなことをするためのモジュールです。

S_AXIから入った信号をM_AXIにスルーしますが、内部でBLOGANA2というモジュールを実装して、AXIのトランザクションをJTAGでキャプチャできるようにするモジュールです。

axi_bram_ctrl

設定は以下のようになっています。データバスの幅は128bitで、アドレス幅(容量)は自動で決まります。

axi_bram_ctrl0_bram

Block Memoryです。この中にデフォルトで256個のBRAMが入っていて、1MByteのRAMを実現しています。

設定は下記のようになっています。多くの項目は自動で設定されるため、ユーザが設定する箇所はありません。

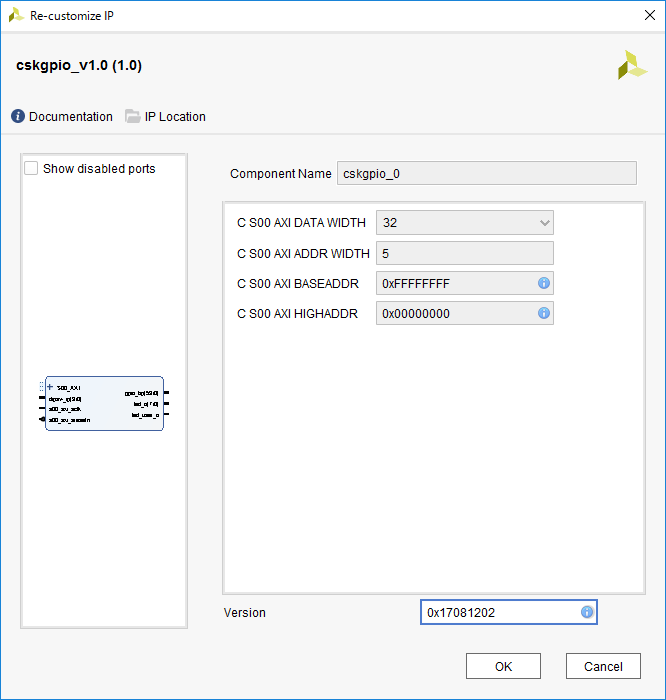

csk_gpio

AXI Slaveポートを備えたGPIOモジュールです。

実質的にBAR0へのアクセスはこのモジュールで処理されます。

ダブルクリックするとプロパティを出すことができ、Versionに設定した値はBAR0の0番地で読み出すことができます。

cosmok_misc

LEDのコントロールなど雑多な機能を実装します。

現時点では下記の機能を持ちます。

- LEDの表示を内蔵レジスタからの出力にするか、それとも各種ステータス表示にするか

- PUSHSWで割り込みを発生させ、IRQ_REQで取り下げる

XDMAコア

XDMA(Xilinx DMA)コアはXILINXが提供するPCI DMAコアです。ホストPCとのメインメモリとの間でDMAを行います。

ポートの説明

XDMAコアのポートの機能を以下に説明します。

| ポート | 機能 |

|---|---|

| M_AXIポート |

DMAが発生すると、からAXIのトランザクションを発行し、M_AXIに接続された周辺回路にバースト転送を発行します。 また、ホストPCのCPUから見たメモリ空間の一部をFPGAにマッピングし、内蔵レジスタや汎用のI/Oを実現しています。 |

|

M_AXI_LITE |

BAR0に割り当てられています。PCかBAR0空間にアクセスすると、M_AXI_LITEのポートからシングルワードのトランザクションが発行され、csk_gpio内のレジスタにアクセスします。 |

| M_AXI_BYPASS | BAR2に割り当てられています。PCからBAR2空間にアクセスすると、M_AXI_BYPASSのポートからマルチワードのトランザクションが発行され、block_ramにアクセスします。 |

| pcie_cfg_mgmt |

FPGA内のユーザロジックから、PCI Expressのコンフィグ空間にアクセスできます。PCIeのコンフィグトランザクションが発生したときに信号が出てくるというものではありません。 |

| sys_clk | 100MHzのクロック入力です。gtxclkモジュールでPCI Expressの差動クロックをシングルエンド信号に変換して入れています。 |

| sys_rst_n | PCI Expressからのシステムリセット入力です。 |

| usr_irq_req[0:0] | ユーザ割り込み入力です。Hになると割り込みを発生させます。 |

| pcie_mgt |

PCI ExpressのTXやRXの信号が入っています。 |

| user_link_up | PCI ExpressがリンクアップするとHになります。 |

| axi_aclk | 125MHzのクロック出力です。AXI用に使います。 |

| axi_aresetn | 負論理のリセット出力です。AXI用に使います。 |

| usr_irq_ack[0:0] | ユーザ割り込みに応答したときにHになります。 |

XDMAコアの設定

XDMAコアをダブルクリックすると設定ダイアログが開きます。

Gen2x4で正しく、かつ、高速で動作するコアを生成するには以下のように設定します。

1ページ目

- Mode・・・Basic

- PCIe Block Location・・・X0Y0

- Lane Width・・・x4

- Maximum Link Speed・・・5.0GT/s

- AXI Data Width・・・128bit

- AXI Clock Frequency・・・125

125MHz 128bitなので2GB/sの帯域となる

64bitにすると250MHzになるが、Kintex-7で250MHzはちょっと厳しい - DMA Interface option・・・AXI Memory Mapped

- AXI Lite Slave Interface・・・オフ

これを有効にするとDMAコントロールレジスタをFPGA内部から操作して、PCI Express経由で勝手にホストPCのメインメモリを操作できると思われるが、そのような使い方は想定していない。

2ページ目

- Vendor ID・・・1BC8 特殊電子回路㈱のベンダID

- Device ID・・・1096 Cosmo-K-のデバイスID

- Revision ID・・・00

- Subsystem Vendor ID・・・1BC8 特殊電子回路㈱のベンダID

- Subsystem Device ID・・・1096 Cosmo-K-のデバイスID

- クラスIDなどは下記の図のように設定する(110000)

Cosmo-K+やCosmo-K0の場合は以下の値にしてください。

| 製品名 | ベンダID | デバイスID |

|---|---|---|

| Cosmo-K- | 1BC8 | 1096 |

| Cosmo-K+ | 1BC8 | 1097 |

| Cosmo-K0 | 1BC8 | 1078 |

3ページ目

- PCIe to AXI Lite Master Interface・・・オン

- 64bit Enable・・オン

- Size・・1M Bytes (任意)

- PCIe to DMA Interface

- 64bit Enable・・オン

- PCIe to DMA Bypass Interface・・・オフ

PCIe to DMA Bypassを有効にすると一部のPCで起動しなくなります- 64bit Enable・・オン

- Size・・512M Bytes (任意)

4ページ目

- Enable MSI Capability Structure・・・オフ

5ページ目

- デフォルトから特に変更なし

BRAMの容量の設定

BlockRAMの使用量は、Address Editorで設定します。VivadoのBlockDesignでは、アドレスのRangeで示されたサイズのBRAM容量が自動的に確保されます。

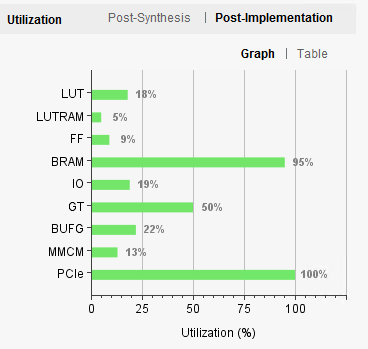

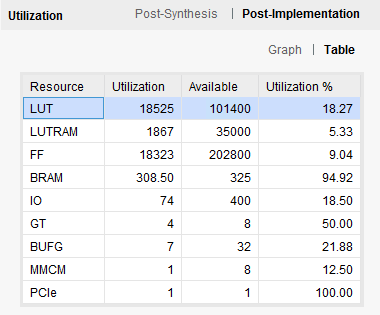

リソース使用量

サンプルデザインを論理合成し、XC7K160Tに実装したときのリソース使用量を以下に示します。

LUTは20%しか使っていないので、まだまだ多くの機能を実装する余裕があります。