DDR3へのDMA

Kintex-7のPCI Express XDMAは、広大なDDR3メモリに対して転送を行って、初めて威力を発揮します。このページではXDMAを使用して、DDR3メモリに読み書きするデザインについて説明します。

ここで紹介するプロジェクトは、BRAMターゲットのPCIe DMAのページで説明したデザインの応用となるので、まずは上記のページをご覧ください。

したがって、主にこのページでは、BRAMターゲットの場合との相違点について紹介します。

→ Vivadoデザインファイルのダウンロードはこちら

ブロックデザイン

まず、完成したブロックデザインを示します。

このデザインには、DDR3メモリを操作するMIGと、PCI Expressを制御するXDMAを中心があります。

AXIバスとクロック

PCI ExpressはGen2 x4で構成されていて、DMA用のM_AXIポートと、制御レジスタ実装用のM_AXI_LITEポートが出力されています。M_AXIポートは64bitのバス幅を持ち、PCI Expressのクロック(axi_aclk)は125MHzとなります。

MIGはDDR3メモリを1600MHz動作(クロック800MHz,データバス32bit)で動作させていて、帯域は6.4GByte/sとなります。MIGのAXI側のバスは256bitとなり、ui_clkは200MHzとなります。

PCIeとMIGはクロックドメインとバス幅が異なるため、間にaxi_interconnectを置いて、その差を吸収しています。

なお、MIGに供給するクロックソースを作り出しているclk_wizには125MHzのクロックを入れていますが、このクロックは基板上の水晶で作り出したものをmgtclk1_p/nから入力しています。したがって、MIGとPCIeは非同期のクロックドメインで動いています。

もし、MIGとPCIeのクロックを同期させたい場合には、clk_wiz_0のclk_in1入力を、xdmaの出力にあるaxi_aclkに接続してください。

cskgpioの役割

cskgpioは、コントロールレジスタを実装しています。

基本的にはBRAMターゲットのPCIe DMAのページで説明したものと同様の役割をしていますが、MIGを有効にすると発熱が大きくなるため電圧や温度を読み出すためのレジスタや、MIGを停止させるためのレジスタが追加されています。

内蔵レジスタのアドレスと機能を以下に示します。

| オフセット | 方向 | 名称 | 機能 |

|---|---|---|---|

| +0 | R | VERSION | バージョン番号 |

| +4 | RW | SW_LED | ボード上のDIPSWやLED |

| +8 | RW | GPIO0_OUT | GPIO[29:0]の出力値 |

| +12 | RW | GPIO0_DIR | GPIO[29:0]の出力許可 |

| +16 | R | GPIO0_IN | GPIO[29:0]の入力値 |

| +20 | RW | GPIO1_OUT | GPIO[59:30]の出力値 |

| +24 | RW | GPIO1_DIR | GPIO[59:30]の出力許可 |

| +28 | R | GPIO1_IN | GPIO[59:30]の入力値 |

| +32 | R | XADC_TEMPE | 温度の読み出し |

| +36 | R | XADC_VCCINT | VCCINTの読み出し |

| +40 | R | XADC_VCCAUX | VCCAUXの読み出し |

| +44 | RW | MIG_CTRL | MIG状態の制御 |

| +48 | RW | IRQ_ENABLE | 割り込みの許可 |

| +52 | RW | IRQ_ASSERT | 割り込み発生 |

MIG_CTRLレジスタの機能は、

- bit0・・・(RW) MIGのリセット信号 0:リセット解除 1:リセット

- bit1・・・(R) MMCM DONEの状態 MIGのクロックがロックしたか?

- bit2・・・(R) MIGのINIT DONEの状態 MIGの初期化が完了したか?

- bit3・・・(RW) MIGのクロック選択 (未使用)

- bit4・・・(RW) MIGのクロックリセット clk_wiz_0をリセットする

となっています。

なお、cskgpioの中でXADCを使用しているため、MIGコアに温度情報を与えなければなりません。そのため、temp_o[11:0]を出力しています。

オフセット+48と+52のレジスタは、割り込みをコントロールするためのレジスタですが、ドライバが操作するため、ユーザが操作する必要はありません。

M_AXI_BYPASSについて

XDMAの設定でPCIe to DMA Bypass Interfaceを有効にすると、M_AXI_BYPASSというポートが作られますが、これを有効にしてポートを未接続のまま開放しておくと、PCによってはOSが起動しないという現象が発生します。

すべてのPCで不具合が生じるわけではなく、正常に動作するPCもあります。

したがって、M_AXI_BYPASSは無効にすることが望ましいといえます。

アドレスの割り当て

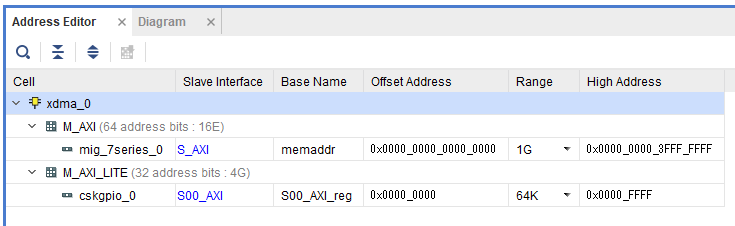

Address Editorで以下のように割り当てます。

M_AXIの0~0x3fffffffをMIG(DDR3)に割り当て、M_AXI_LITEの0~0xffffをCSKGPIOに割り当てています。

DMA速度

PCIe Gen2 x4で行った場合、Read/Writeともに1.6~1.7GB/secの速度が出ています。概ね10M~100MByteのときに最高の速度となるようです。

BRAMとDDR3メモリに有意な差はみられませんでした。DDR3の読み出しオーバーヘッドなどによる速度の低下は観測できませんでした。

エラー率

PCIe経由でDDR3メモリに22TByte転送しましたが、1bitのエラーも発生しませんでした。

単純な計算によれば、エラー率は5.6×10-15以下と見積もれます。

デバイスドライバと制御ソフト

こちらのページをご覧ください。

ライセンス

このサンプルプロジェクトおよび、当社製のライブラリは当社のComso-Kで使用する上では自由に使用できます。エンドユーザへの再配布も可能です。

Cosmo-Kではなく、お客様が開発したハードで使用する場合も基本的に無償で使用できますが、無保証であることの確認のため、あらかじめご連絡ください。