カスタマイズ方法

CoreGenラッパとカスタマイズ方法

GTPや内蔵エンドポイントに、パラメータを与えているのはCoreGenラッパです。

ここでいうパラメータというのは、例えば、PCI ExpressのベンダIDや、BARの構成、それからGTP(ギガビットトランシーバ)の送出振幅レベルや入力イコライザの設定などがあります。

こういったパラメータは、CoreGenラッパ内で生成されます。

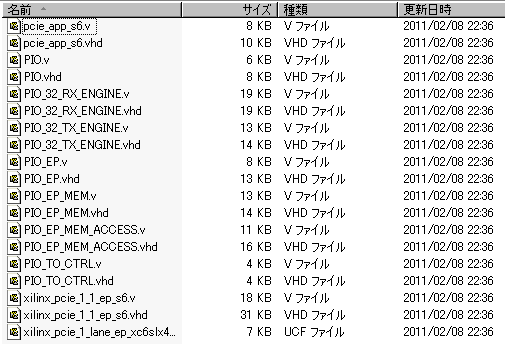

CoreGenラッパの実体は、プロジェクトフォルダ¥ipcore_dir¥eptest¥source のディレクトリにある各種のVHDLファイル(またはVファイル)です。

ISEは、プロジェクトに登録されているeptest.xcoファイルの実体である、これらのファイルを参照して論理合成します。CoreGenは、これらのファイルを生成します。したがって、これらのファイルを直接書き換えることでもGTPやPCIEの動作を書き換えることができます。(※しかし、CoreGenで再び「生成」すると手動で書き換えたところは消されてしまいます)

CoreGenラッパの再生成

ここでは、ベンダIDやBARの設定を書き換える方法を例に、CoreGenでのコアの再生成のやりかたを説明します。

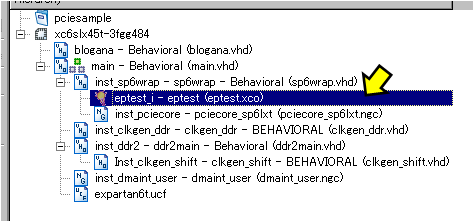

まず、ISEのプロジェクトツリー画面で、coregenのアイコンであるeptest_iをダブルクリックします。

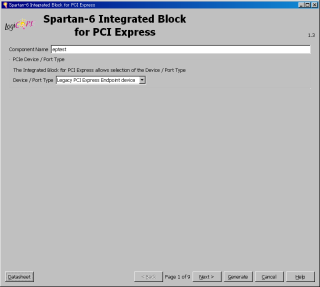

しばらくすると、CoreGeneratorの画面が開くので、最初のダイアログではNextを押します。

CoreGeneratorの最初のダイアログ(クリックで拡大)

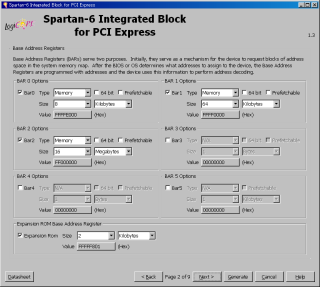

次に、BAR設定のダイアログが開きます。

サンプルプロジェクトのデフォルトではBAR0=8kバイト、BAR1=64kバイト、BAR2=16Mバイトとなっています。

また、拡張ROM領域として2Kバイトの領域を取得しています。

これらの値を、お客様のデザインに合わせた値に書き換えてください。

BAR設定のダイアログ(クリックで拡大)

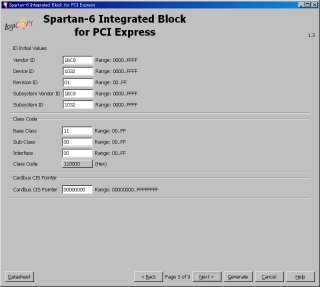

Nextを押すと、ベンダID・デバイスID設定のダイアログが開きます。

1BC8というのが特殊電子回路のベンダIDなので、カスタマイズしたい場合には書き換えます。

クラスコードというのは、PCI Expressカードの種類(ネットワークカード,グラフィックカード,データ収集装置などの分類)を示すものです。基本的には何でもいいのですが、グラフィックカードとかの値をセットすると、BIOSが起動時にそのカードを使おうとしてしまうので、起動できなくなりますので、避けたほうがいいでしょう。

サンプルデザインでは110000(HEX)という「汎用データ収集装置」のコードをセットしています。

ベンダID・デバイスID設定のダイアログ(クリックで拡大)

それから、しばらくNextを押していくといろいろなダイアログが開きますが、途中のダイアログでは特に設定すべき箇所はありません。

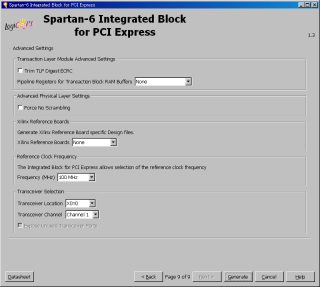

最後のダイアログは、物理層関係の設定が行われます。

ここではリファレンスクロックが100MHzか、125MHzかという設定と、トランシーバのチャネルを設定します。

物理層の設定ダイアログ(クリックで拡大)

EXPARTAN-6Tでは、リファレンスクロックは100MHzです。 (XILINXのSP605では125MHz)

また、EXPARTAN-6TではGTPのX0Y0ブロックにはPCI Expressが、X0Y1ブロックにはSATAが接続されています。したがって、ここではX0Y0を選びます。

X0Y0のChannel1にはPCI Expressカードエッジが、X0Y0のChannel0にはExternal Cablingが接続されています。カードエッジ側で使う場合は、X0Y0のChannel1にしておきます。

CoreGenでは設定できない項目の変更

CoreGenでは、トランシーバの出力レベルを変更できません。

また、ディエンファシス(プリエンファシス)も設定できません。

ところが、CoreGenが生成するラッパでは、プリエンファシスがゼロに設定されているので、PCI Expressの波形的に正しいものになっていません。

したがって、プロジェクトフォルダ¥ipcore_dir¥eptest¥source の中にあるgtpa1_dual_wrapper_tile.vhd(もしくはgtpa1_dual_wrapper_tile.v)を開いて、TXDIFFCTRL0、TXDIFFCTRL1、TXPREEMPHASIS0、TXPREEMPHASIS1を次のように書き換える必要があります。

TXDIFFCTRL0 => "1001", -- 1110mV

TXDIFFCTRL1 => "1001", -- 1110mV

・・・

TXPREEMPHASIS0 => "100", -- 3.5dB

TXPREEMPHASIS1 => "100", -- 3.5dB

この設定を行わない場合と、行わなった場合の効果については、高速シリアル波形のページをご覧下さい。

Copyright(C) 2009 TokushuDenshiKairo Inc. All rights reserved.